CMRI-Bus-Interface

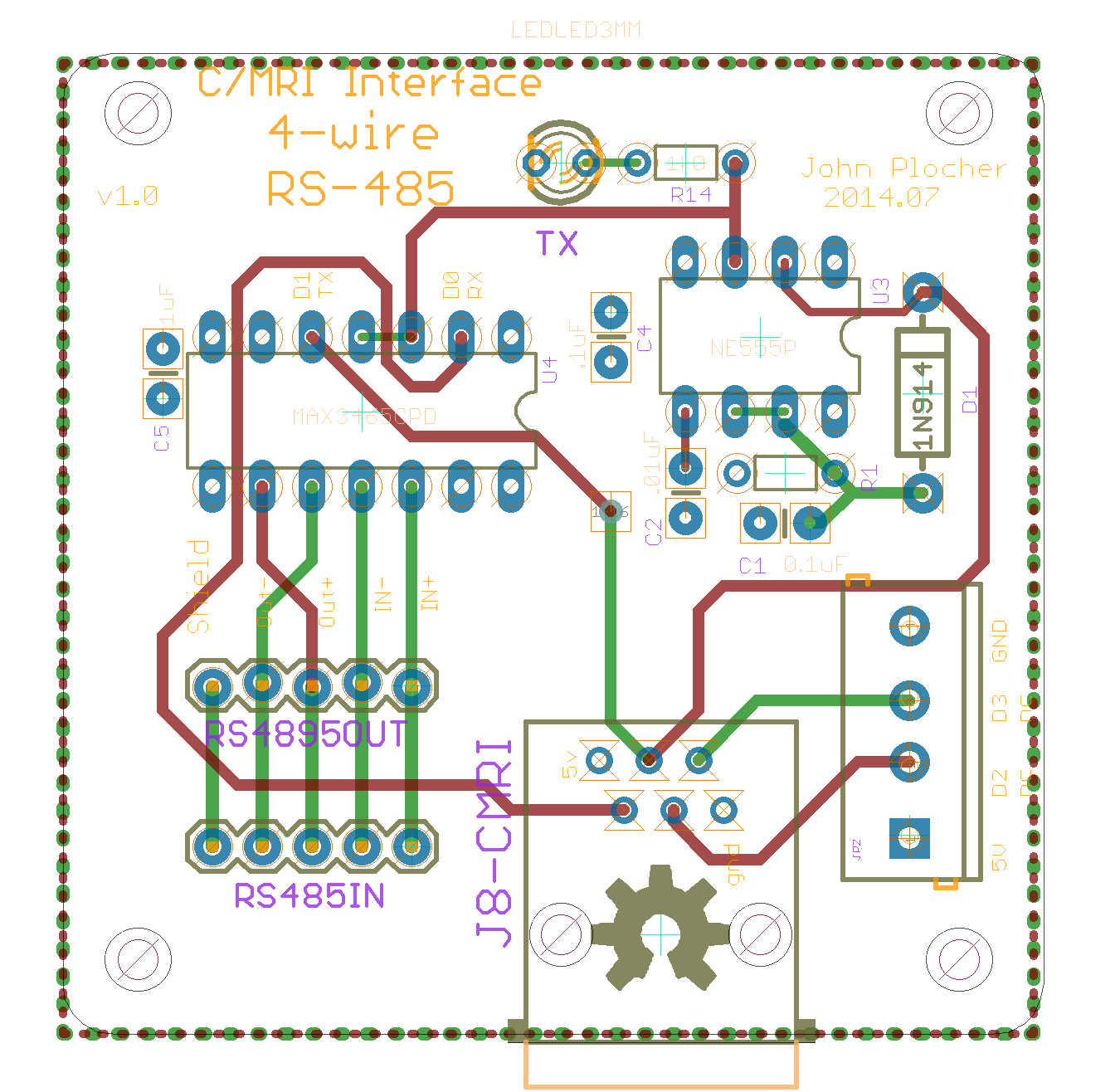

RS422/485 driver for CMRI-Net

Pin-header interface

Daughter board for interfacing with CMRI Bus traffic using MRCS ‘duino example code. Uses an optional onboard 555 to generate TX/RX enable based on processor I/O direction

|

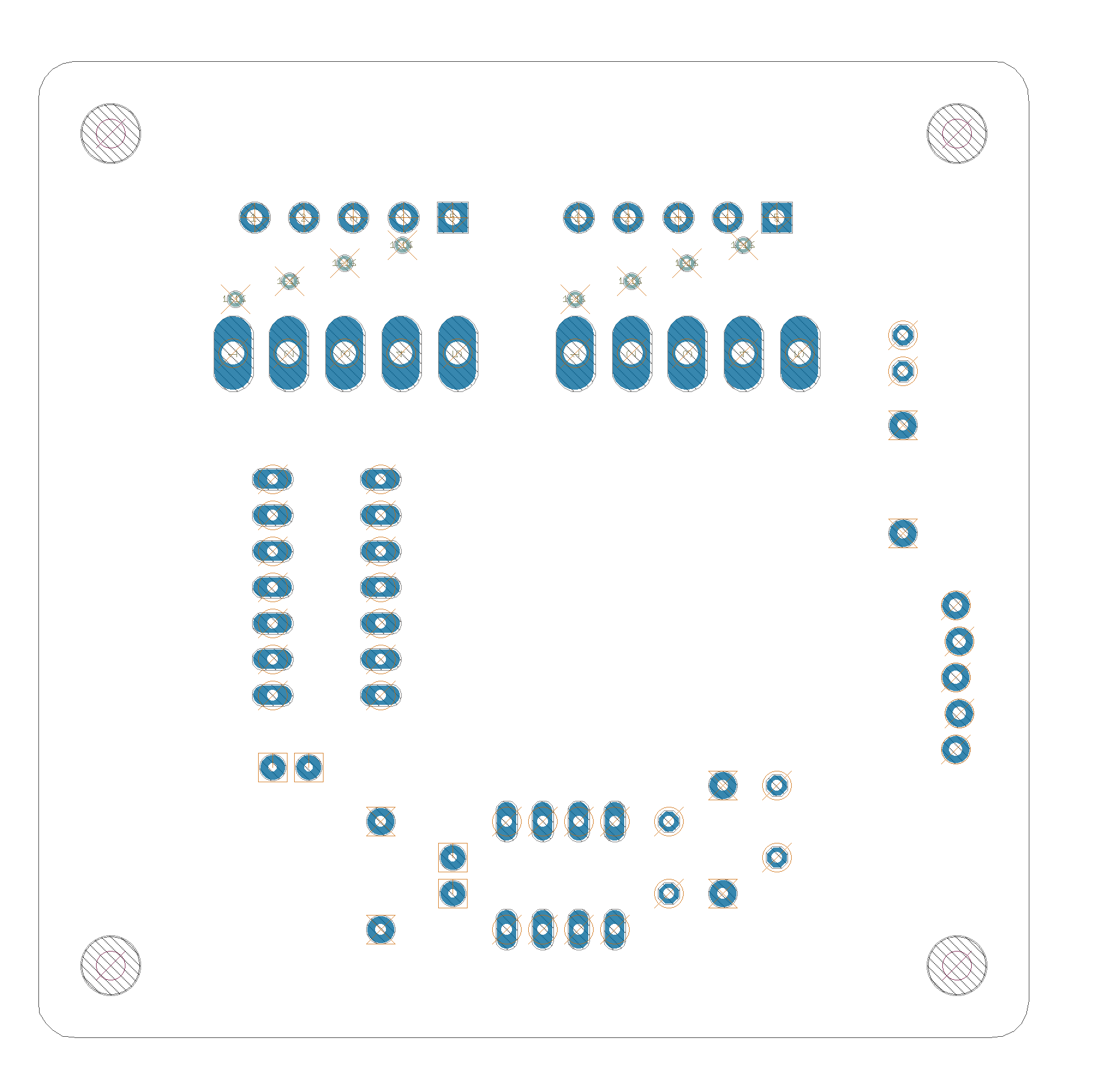

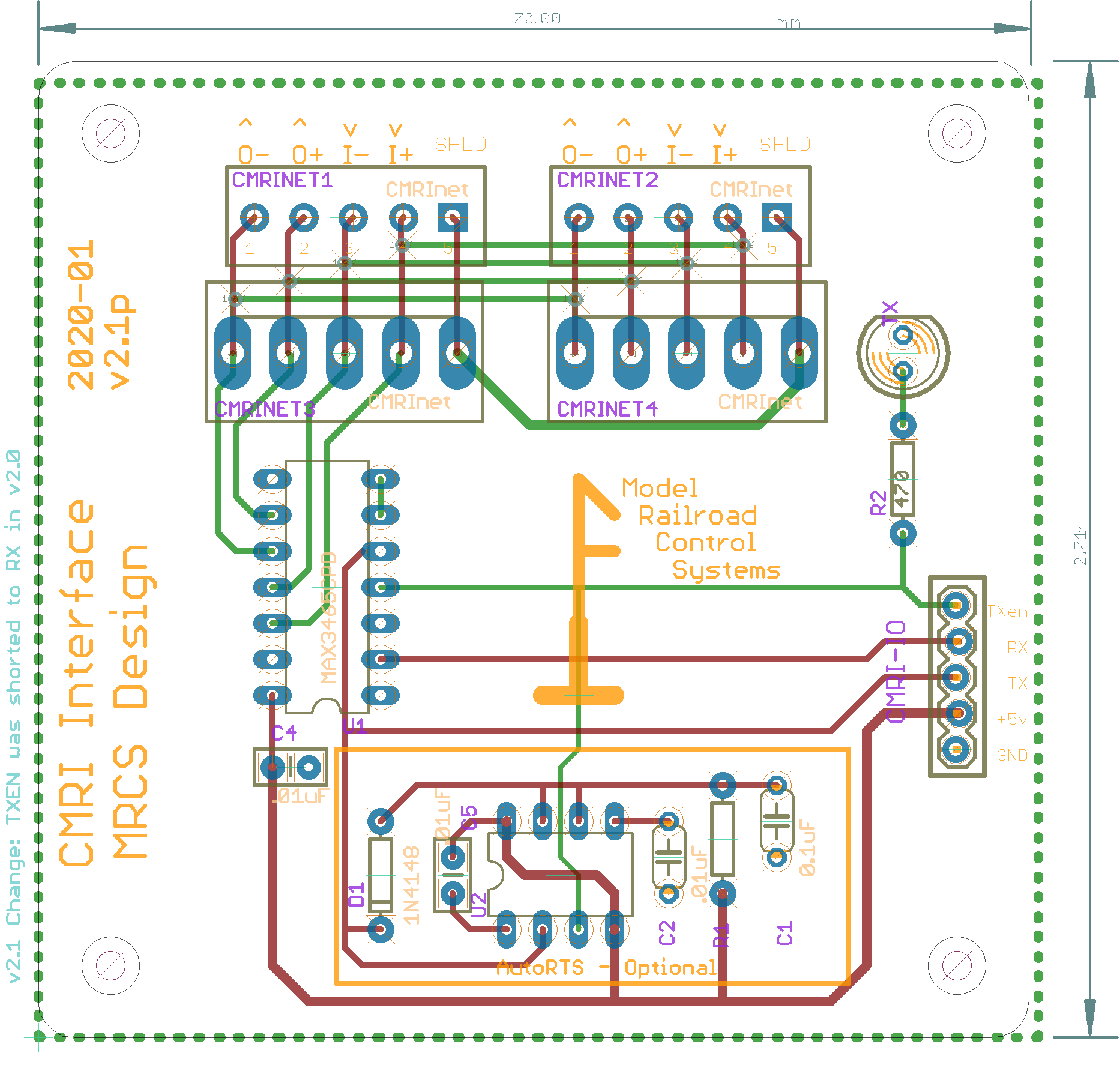

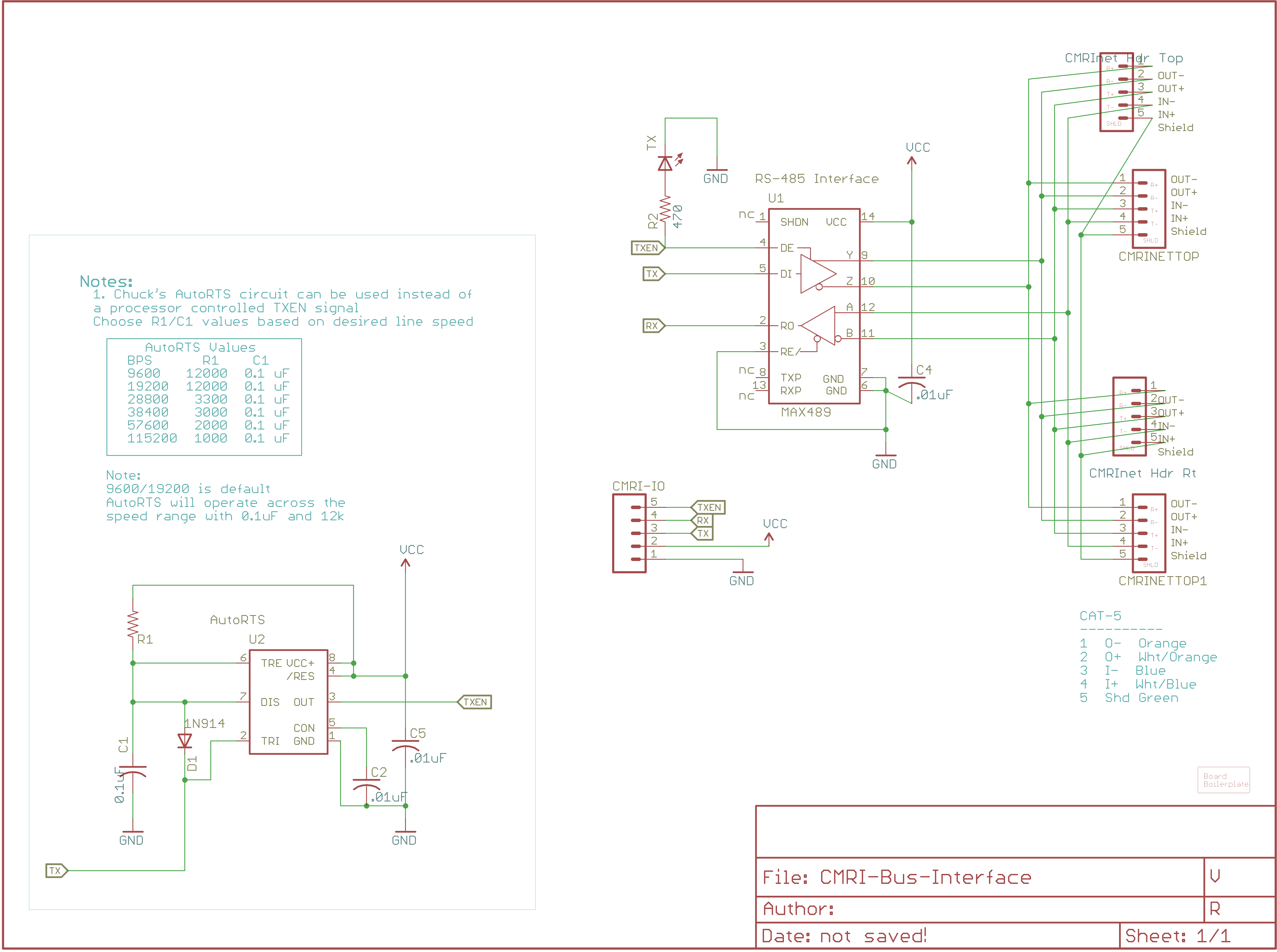

CMRI-Bus-Interface Version 2.1

Not built

Pin-header interface

Daughter board for interfacing with CMRI Bus traffic using MRCS ‘duino example code. Uses an optional onboard 555 to generate TX/RX enable based on processor I/O direction

|

|

|

UNPUBLISHED

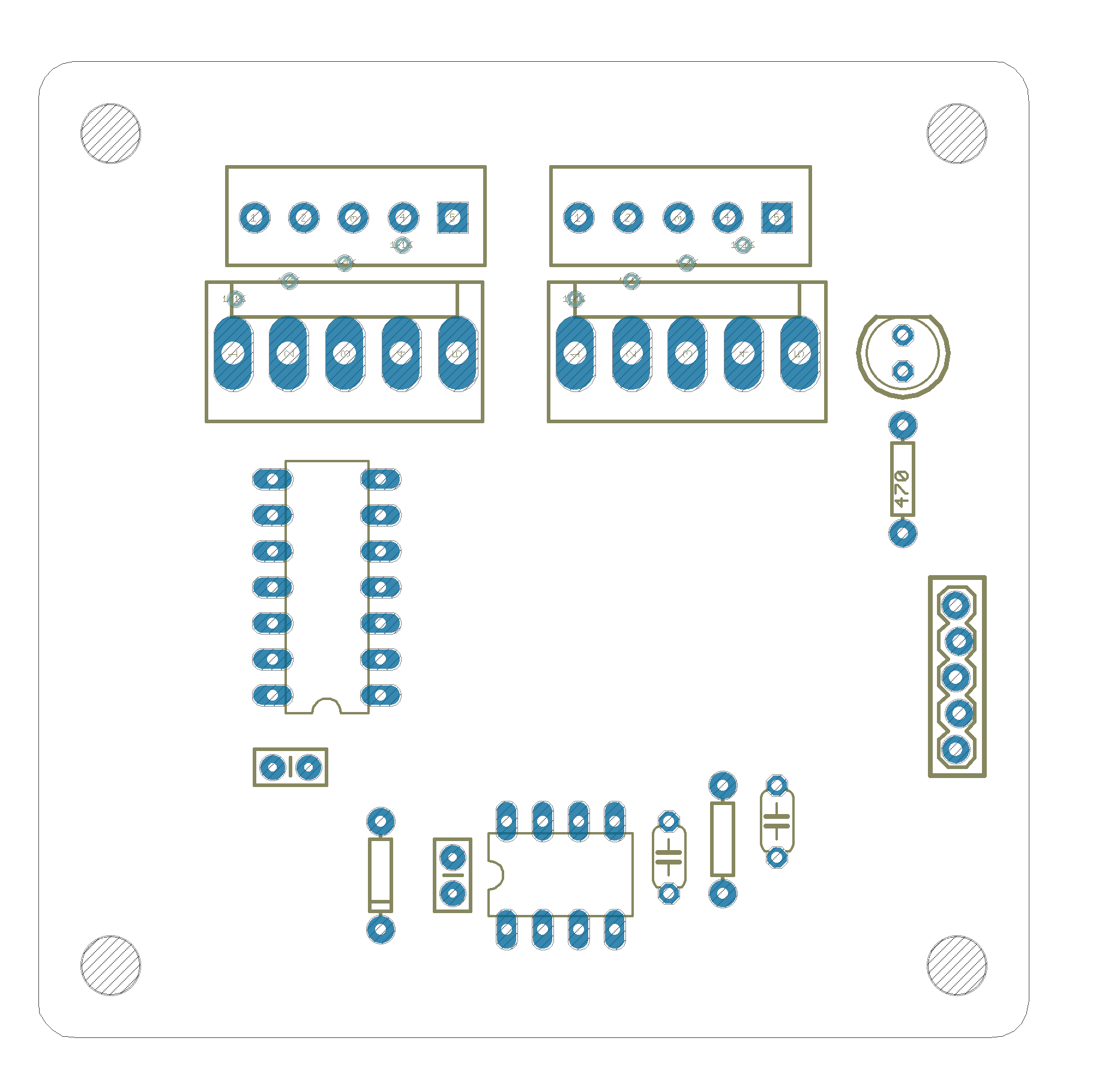

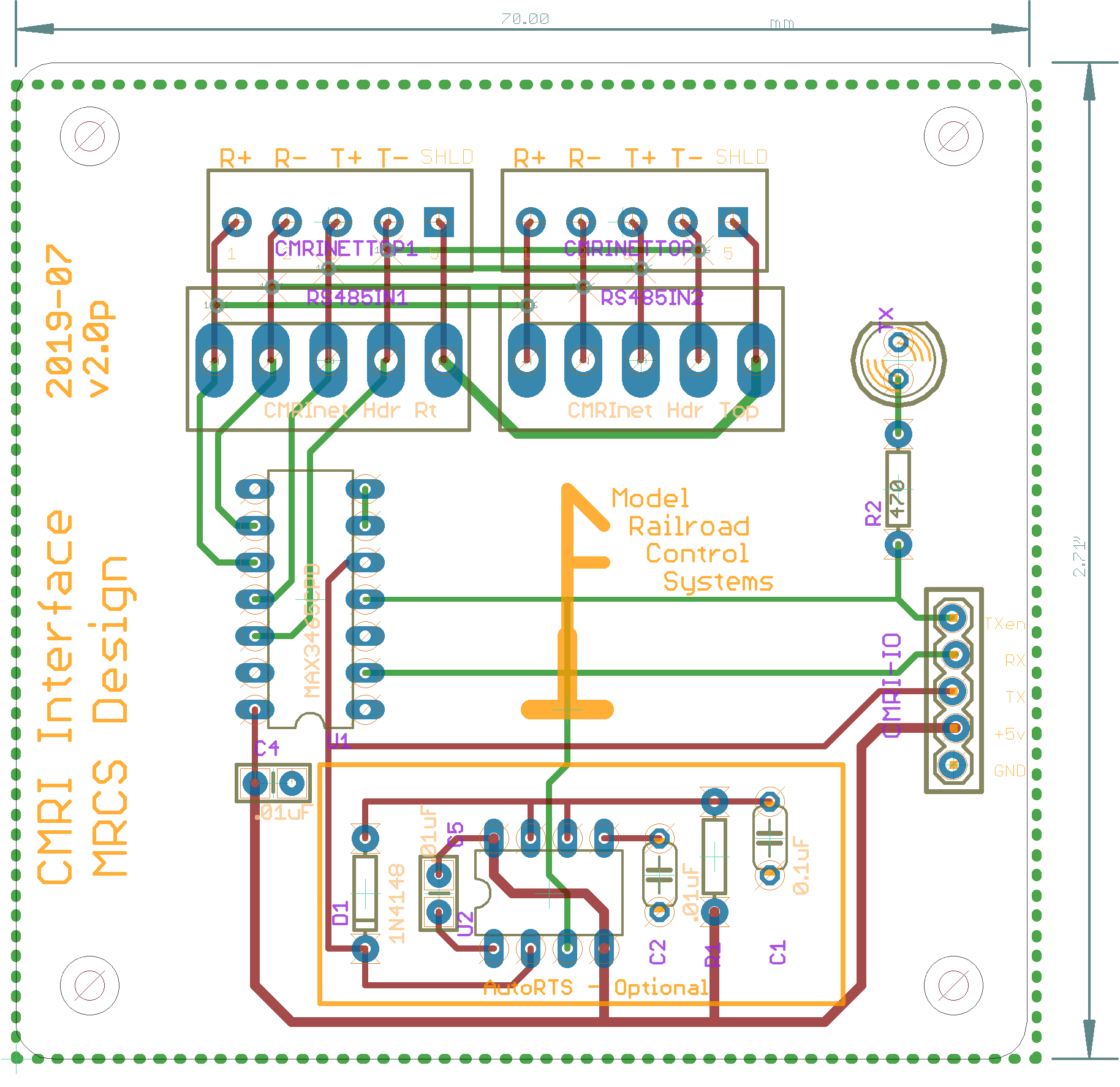

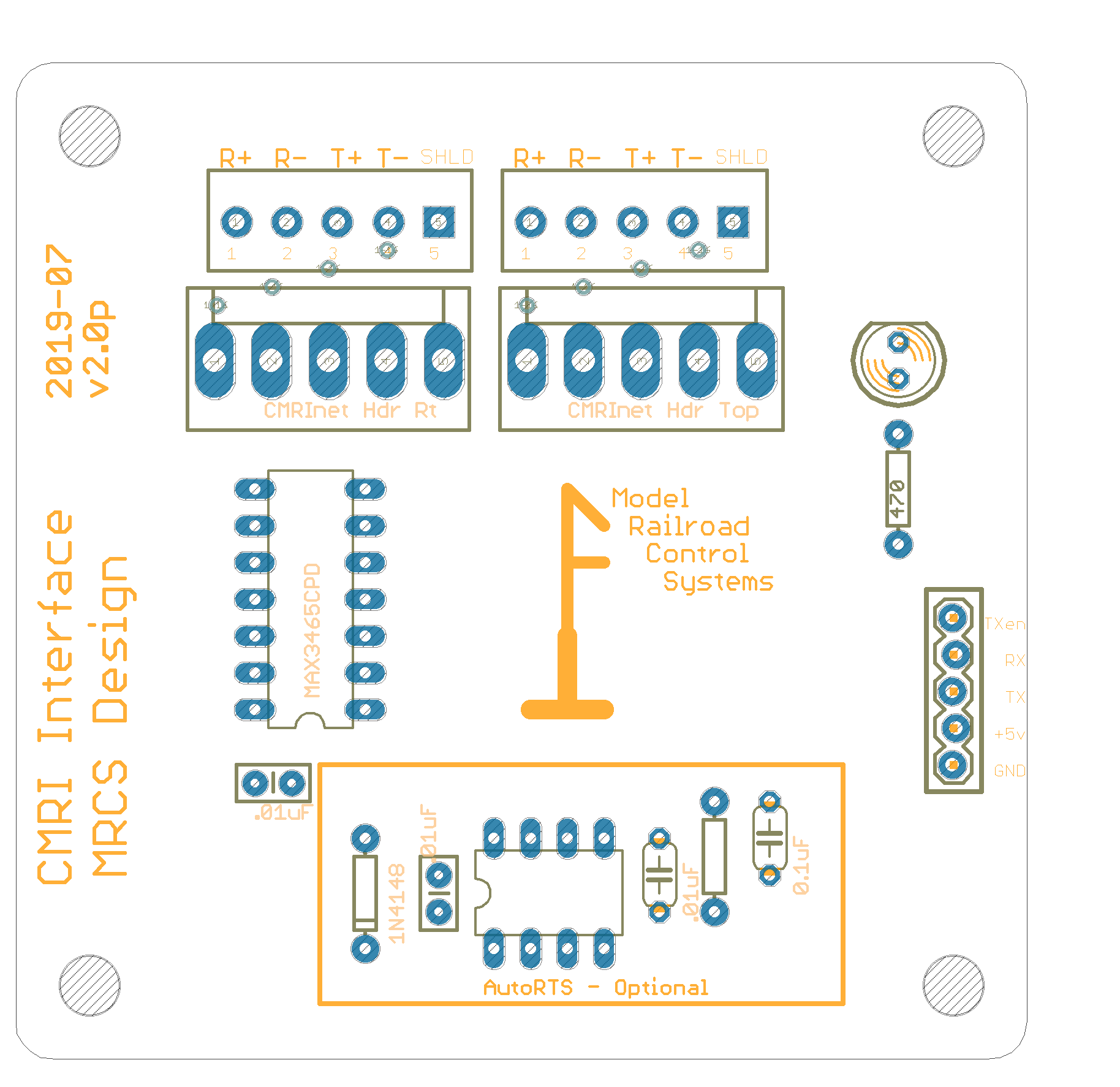

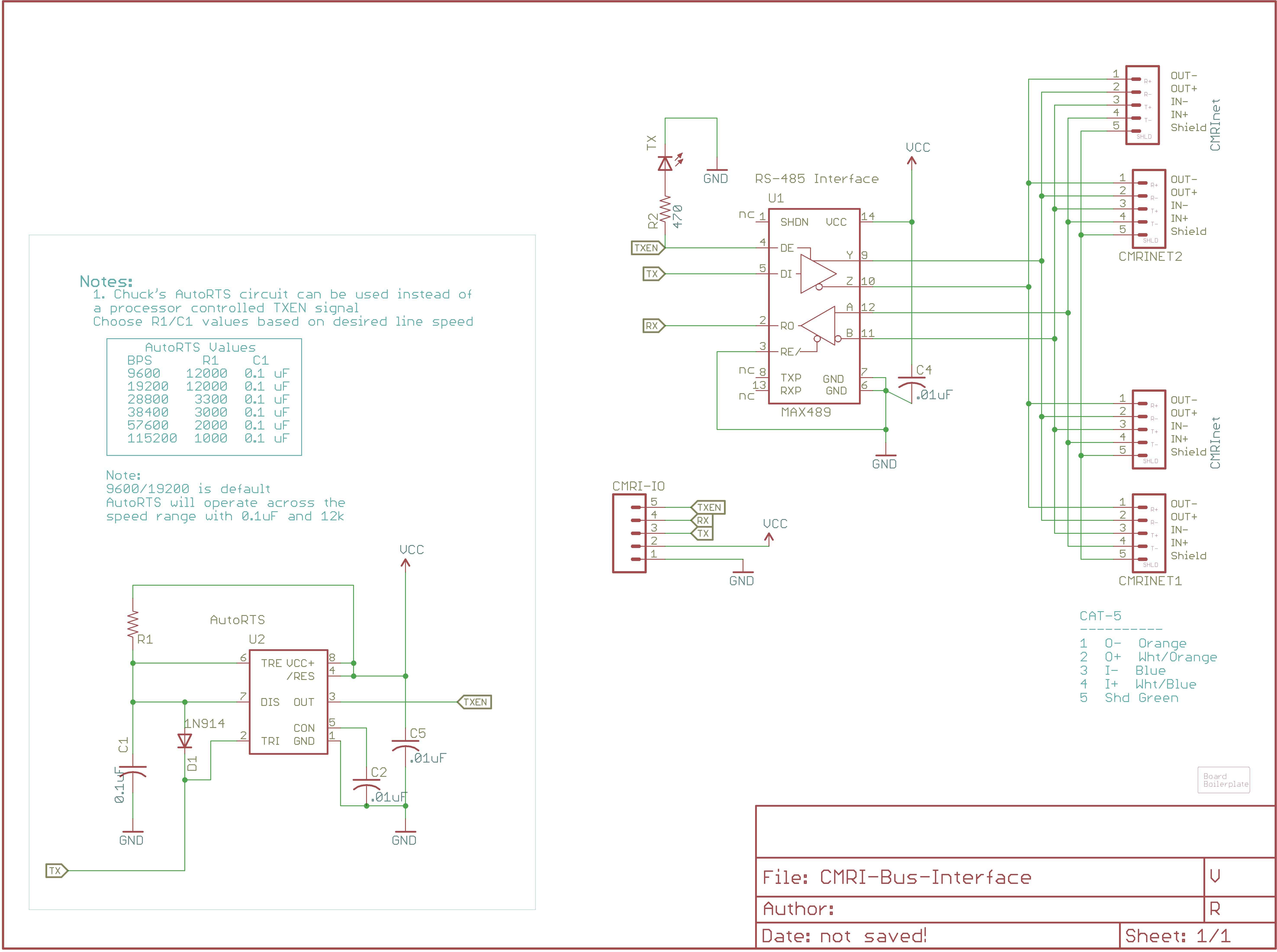

CMRI-Bus-Interface Version 2.0

Not built

Pin-header interface

Daughter board for interfacing with CMRI Bus traffic using MRCS ‘duino example code. Uses an optional onboard 555 to generate TX/RX enable based on processor I/O direction

|

|

|

UNPUBLISHED

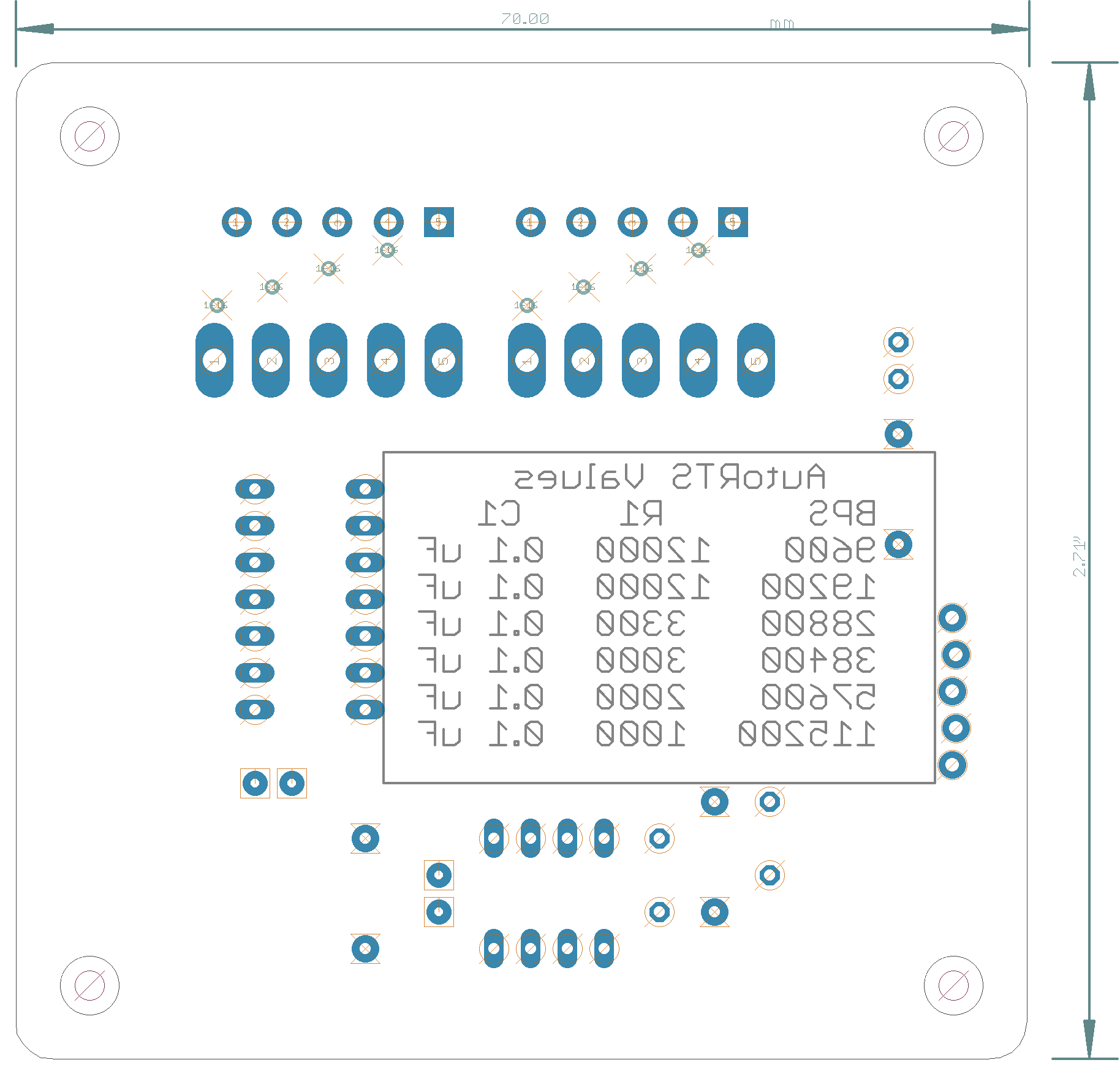

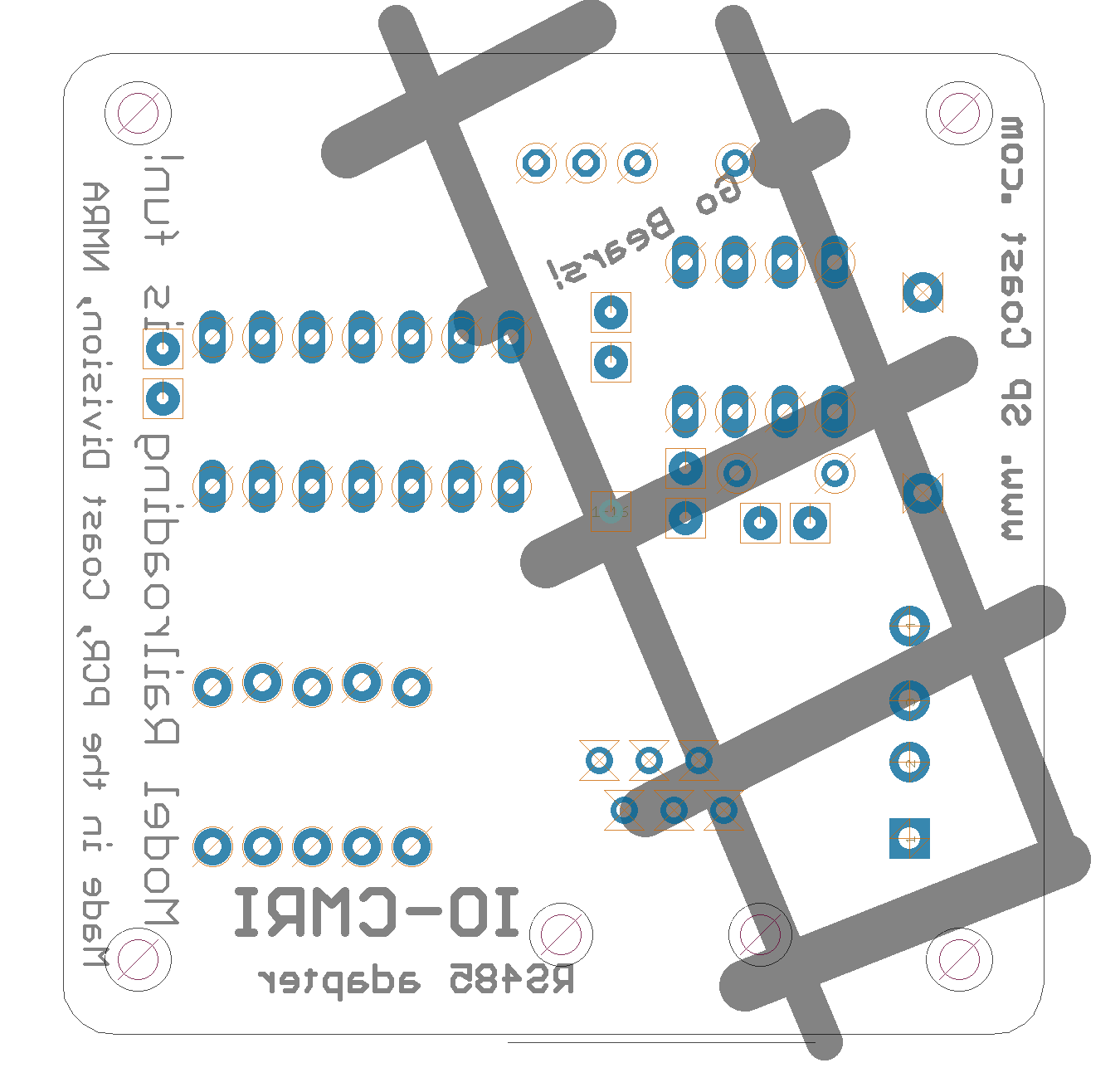

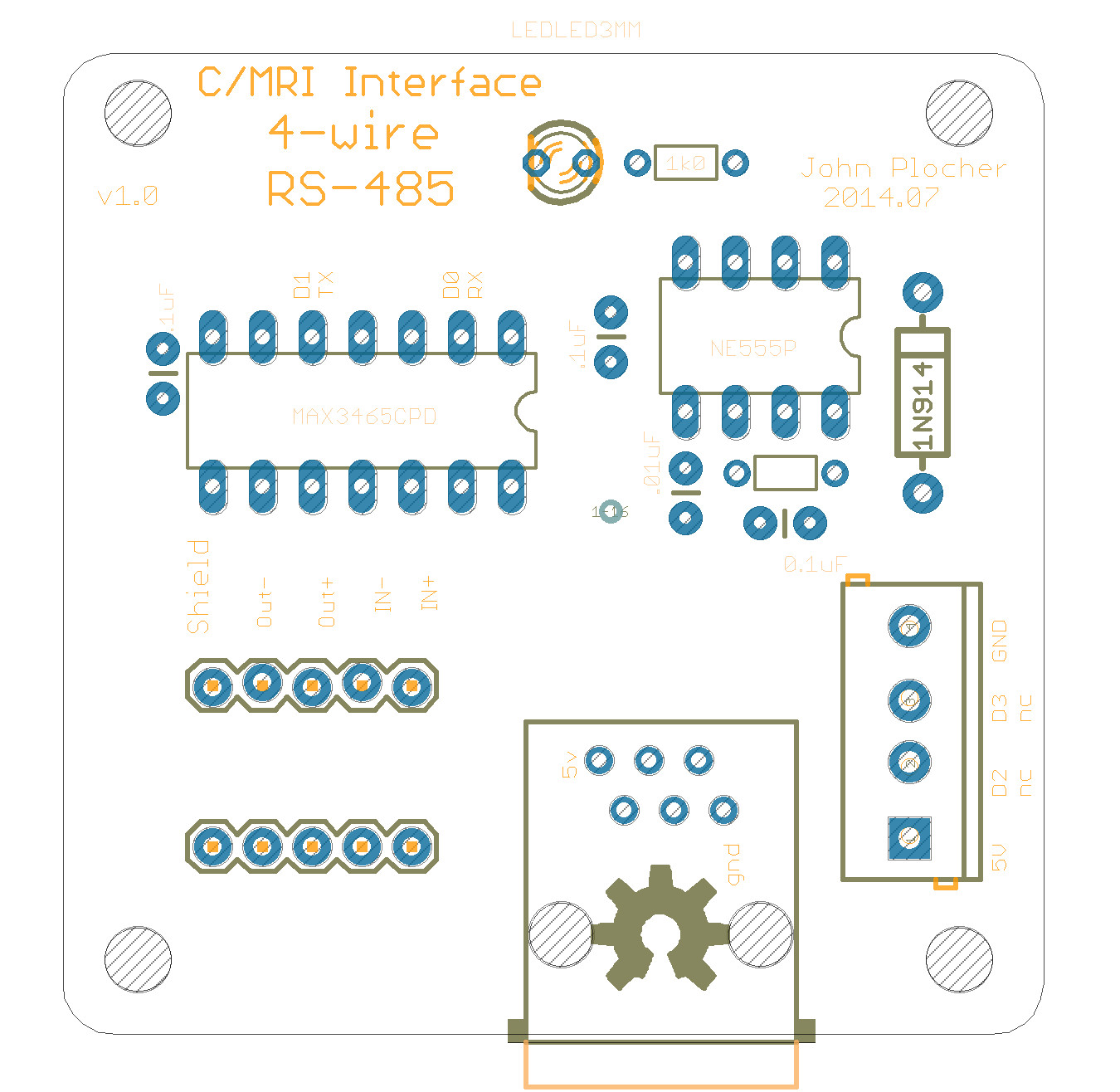

CMRI-Bus-Interface Version 1.0

Not built

IO4 interface

Daughter board for interfacing with CMRI Bus traffic using MRCS ‘duino example code. Uses an optional onboard 555 to generate TX/RX enable based on processor I/O direction

|

|

|

UNPUBLISHED

This technical documentation is licensed under the CERN Open Hardware Licence v1.2